# Fully-Integrated Bi-directional PD3.0 and Fast Charge Power Bank SOC with Multiple Input and Output Ports

### Features

- Support multiple ports simultaneously

- ♦ 2 USB A output ports

- ♦ 1 USB B input port

- ♦ 1 USB C input/output port

- Fast charge

- ♦ Every port support fast charge

- ♦ Support QC2.0/QC3.0 output

- ♦ Qualcomm Certificate No.: 4788056908-2

- ♦ Support FCP input/output

- ♦ Support AFC input/output

- ♦ Support SFCP input/output

- ♦ Support MTK PE1.1&2.0 output

- ♦ Support USB C DRP input/output

- ♦ Support BC1.2, Apple, Samsung

- Integrated USB Power Delivery (PD2.0/PD2.0) protocol

- Support PD2.0 bi-directional input/output protocol

- ♦ Support PD3.0 input/output and PPS output

- protocol

- ♦ Support 5V, 9V, 12V voltage input/output

♦ PPS support 5~12V adjustable voltage with

- 20mV/step ♦ Integrate hardware biphase mark coding BN

- Integrate hardware biphase mark coding (BMC) module

- Integrate physical (PHY) layer for TX/RX across the CC wire

- ♦ Integrate hardware CRC calculation module

- ♦ Support hard reset

- Charger

- ♦ Up to 5.0A charging current at battery port

- ♦ Adaptive charging current adjustment

- ♦ Support 4.20V, 4.35V, 4.40V, 4.50V batteries

- Discharger

- ♦ Current output capacity:

- ♦ 5V: 3.1A 9V: 2.0A

- Up to 95% @ 5V/2A discharge efficiency of Synchronous switching

12V: 1.5A

- Support line compensate

- Battery level display

- ♦ Integrated 14-bit ADC and coulometer

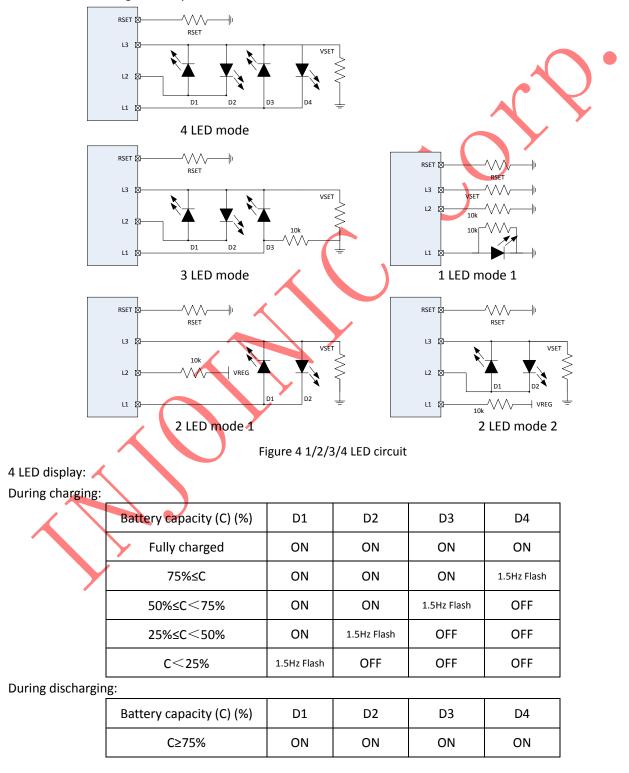

- ♦ Support 1/2/3/4 LED battery indicator

- ♦ Auto recognition of LED number

- $\diamond$  Adjustable battery level curve, uniform brightness

- Others

- $\diamond \qquad \text{Integrated torch-light driver}$

- ♦ Support auto detect of plug in and out

- ♦ Fast charge status indicator

- ♦ Support key control

- ♦ Enter standby mode automatically in light load

#### Multiple protection, high reliability

> Input overvoltage and under voltage protection

- Output overcurrent, overvoltage and short circuit protection

- Battery overcharge, over discharge and overcurrent protection

- ♦ Over temperature protection

- ♦ Battery NTC protection

- $\diamond$  4KV ESD, input voltage up to 25V (including CC pins)

- Simplified BOM

- ♦ Integrated switch power MOSFET

- ♦ Single inductor for charging and discharging

- In-depth customization

- I2C interface for flexible and low cost customized solution

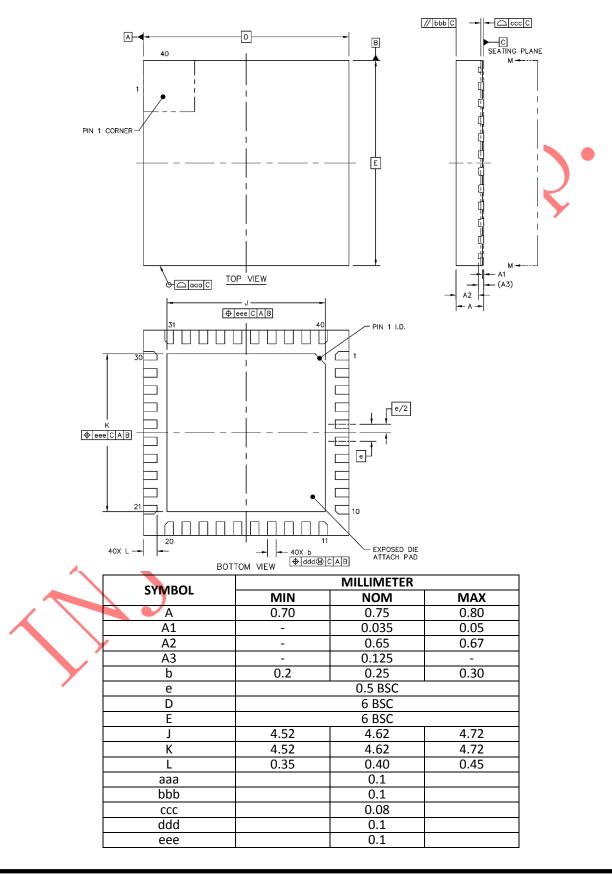

- Package pin to pin with IP5328

- Package size: 6mm\*6mm, 0.5mm pitch, QFN40

## Applications

- Power Bank, Portable Charger

- Smart Phones, Tablets and Portable devices

## Description

IP5328P is a fast charge power management SOC for total solution on fast charge Power Bank. IP5328P support QC2.0/QC3.0 output, FCP/AFC/SFCP input/output, MTK PE+ 1.1&2.0 output, USB C/PD2.0/PD3.0 input/output, USBC PPS output, BC1.2/Apple/Samsung; it integrate Li-battery charging and discharging management, support battery level display, etc. Four USB ports can work simultaneously, 2\*USB A, USB B and USB C, each port support fast charge when working alone, 5V mode for two or more ports working state.

IP5328P are highly integrated with abundant function, support Buck and Boost with one single inductor, along with few peripheral devices make the total solution size minimized and BOM cost down.

IP5328P supply up to 18W output ability using synchronized switch boost system, efficiency is higher than 90% for 18W output even when the battery voltage is low. If no load detected, the system enters standby mode automatically.

IP5328P synchronized switch charging system supply up to 5.0A charging current. In control of IC and battery temperature and input voltage loop, intelligently adjust charging current.

IP5328P integrate USB C standard, support USB C, PD2.0 and PD3.0 protocol.

IP5328P integrate 14-bit ADC, ADC data can be accessed through I2C interface. Together with internal coulometer and algorithm for accurate battery voltage and current measurement. Battery level curve can be customized for precise battery level display.

IP5328P support battery level display on 1/2/3/4 LED, auto-detect display mode; support torch light; support key function.

Customized functions: charging battery and phones at the same time, PD15V output, charging for wearable devices.

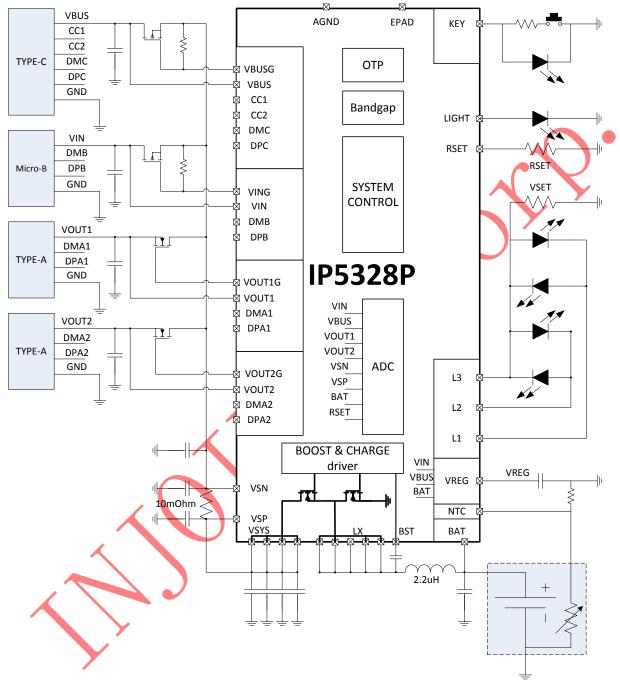

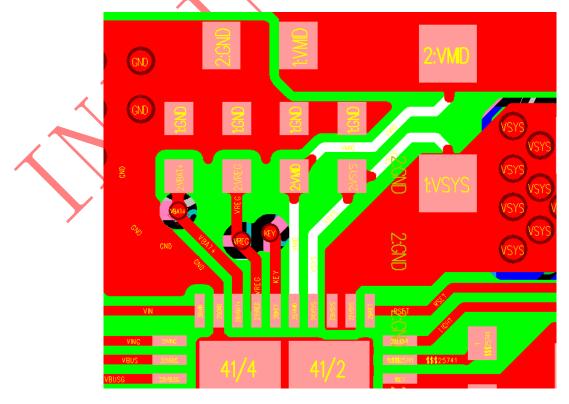

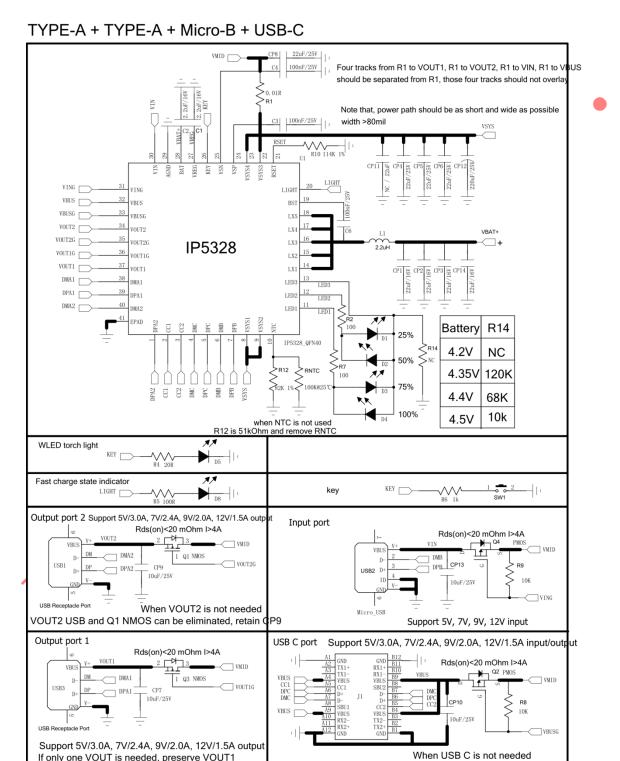

# **Typical Application**

Figure 1 Simplified Application Diagram (4 LED for Battery Level Display)

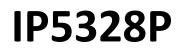

### 1. Pin Definition

Figure 2 IP5328P Pin Assignments

| Pin Num        | Pin Name | Description                                                                                                        |  |  |  |

|----------------|----------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1              | DPA2     | DP data line on VOUT2 USB port                                                                                     |  |  |  |

| 2              | CC1      | CC1 line on USB C port                                                                                             |  |  |  |

| 3              | CC2      | CC2 line on USB C port                                                                                             |  |  |  |

| 4              | DMC      | DM data line on USB C port                                                                                         |  |  |  |

| 5              | DPC      | DP data line on USB C port                                                                                         |  |  |  |

| 6              | DMB      | DM data line on Micro USB port, reused as I2C2 SCK                                                                 |  |  |  |

| 7 🔨            | DPB      | DP data line on Micro USB port, reused as I2C2 SDA                                                                 |  |  |  |

| 8/9/22/23      | VSYS     | Public Node of system input and output                                                                             |  |  |  |

| 10             | NTC      | NTC Resistor input for battery temperature sense                                                                   |  |  |  |

| 11             | L1       | Battery level display drive pin L1, reused as I2C1 SCK                                                             |  |  |  |

| 12             | L2       | Battery level display drive pin L2, reused as I2C1SDA                                                              |  |  |  |

| 13             | L3       | Battery level display drive pin L3, reused as VSET, used for MCU wake up output pin during I2C1 mode               |  |  |  |

| 14/15/16/17/18 | LX       | DCDC switch node, connect to inductor                                                                              |  |  |  |

| 19             | BST      | Internal high voltage drive, serial capacitor to LX                                                                |  |  |  |

| 20             | LIGHT    | Fast charge mode indicator                                                                                         |  |  |  |

| 21             | RSET     | Battery internal resistance compensate, trimming the battery level curve, used as MCU wake up pin during I2C2 mode |  |  |  |

| 24             | VSP      | Positive sample node of VSYS current, separate layout with VSYS                                                    |  |  |  |

| 25       | VSN    | Negative sample node of VYSY current                 |

|----------|--------|------------------------------------------------------|

| 26       | KEY    | Key detect pin, reused as WLED torch light function. |

| 27       | VREG   | 3.1V Voltage output                                  |

| 28       | BAT    | Battery supply pin                                   |

| 29       | AGND   | Analog ground                                        |

| 30       | VIN    | VIN charge detect pin                                |

| 31       | VING   | VIN charge input PMOS control pin                    |

| 32       | VBUS   | VBUS charge detect pin                               |

| 33       | VBUSG  | VBUS charge input PMOS control pin                   |

| 34       | VOUT2  | VOUT2 discharge load detect pin                      |

| 35       | VOUT2G | VOUT2 discharge NMOS control pin                     |

| 36       | VOUT1G | VOUT1 discharge NMOS control pin                     |

| 37       | VOUT1  | VOUT1 discharge load detect pin                      |

| 38       | DMA1   | DM data line on VOUT1 USB port                       |

| 39       | DPA1   | DP data line on VOUT1 USB port                       |

| 40       | DMA2   | DM data line on VOUT2 USB port                       |

| 41(EPAD) | GND    | Power and dissipation ground                         |

## 2. IP Series Products List

#### **Power Bank IC**

|                | Char<br>/Disch | -              |            | Features     |      |     |     |       |                       |               | Package |                   |

|----------------|----------------|----------------|------------|--------------|------|-----|-----|-------|-----------------------|---------------|---------|-------------------|

| IC<br>Part No. | Charge         | Dis-<br>charge | LED<br>Num | Lighti<br>ng | Keys | I2C | DCP | USB C | QC<br>Certifi<br>cate | PD3.0/<br>PPS | Package | Compa<br>tibility |

| IP5303         | 1.0A           | 1.2A           | 1,2        | ٧            | ٧    | -   | -   | -     | -                     | -             | eSOP8   | z                 |

| IP5305         | 1.0A           | 1.2A           | 1,2,3,4    | v            | v    | -   | -   | -     | -                     |               | eSOP8   | PIN2PIN           |

| IP5306         | 2.4A           | 2.1A           | 1,2,3,4    | ٧            | ٧    | -   | -   | -     | -                     | -             | eSOP8   | Ы                 |

| IP5206         | 2A(Max)        | 1.5A           | 3,4,5      | ٧            | ٧    | -   | -   | -     |                       | Y             | eSOP16  | z                 |

| IP5108E        | 2.0A           | 1.0A           | 3,4,5      | ٧            | ٧    | -   | -   |       | -                     | <b>)</b> -    | eSOP16  | PIN2PIN           |

| IP5108         | 2.0A           | 2.0A           | 3,4,5      | ٧            | ٧    | v   | -   | -     |                       | -             | eSOP16  | Ы                 |

| IP5207         | 1.2A           | 1.2A           | 3,4,5      | ٧            | ٧    | -   | -   |       | ).                    | -             | QFN24   |                   |

| IP5207T        | 1.2A           | 1.2A           | 1,2,3,4    | ٧            | ٧    | V   | ٧   | -     | -                     | -             | QFN24   | NId               |

| IP5109         | 2.1A           | 2.1A           | 3,4,5      | V            | ٧    | V   | -   | -     | -                     | -             | QFN24   | PIN2PIN           |

| IP5209         | 2.4A           | 2.1A           | 3,4,5      | ٧            | У    | V   | Y   | -     | -                     | -             | QFN24   |                   |

| IP5219         | 2.4A           | 2.1A           | 1,2,3,4    | V            | V    | V   | V   | ٧     | -                     | -             | QFN24   |                   |

| IP5310         | 3.1A           | 3.0A           | 1,2,3,4    | Х            | V    | V   | ٧   | ٧     | -                     | -             | QFN32   |                   |

| IP5312         | 15W            | 3.6A           | 2,3,4,5    | V            | V    | V   | ٧   | -     | -                     | -             | QFN32   |                   |

| IP5318Q        | 18W            | 4.0A           | 2,3,4,5    | V            | V    | V   | v   | -     | ٧                     | -             | QFN40   | 1                 |

| IP5318         | 18W            | 4.0A           | 2,3,4,5    | V            | ۷    | v   | ٧   | ٧     | ٧                     | -             | QFN40   | PIN2<br>PIN       |

| IP5322         | 18W            | 4.0A           | 1,2,3,4    | V            | v    | V   | v   | -     | ٧                     | -             | QFN32   |                   |

| IP5328         | 18W            | 4.0A           | 1,2,3,4    | V            | v    | v   | v   | ٧     | ٧                     | -             | QFN40   | 12                |

| IP5328P        | 18W            | 4.0A           | 1,2,3,4    | V            | v    | v   | v   | ٧     | ٧                     | ٧             | QFN40   | PIN2<br>PIN       |

## USB Charging Port Control IC

|                   |         |                     |                     |     |     | Sta | ndards S | upported           |       |     |                        |       |         |

|-------------------|---------|---------------------|---------------------|-----|-----|-----|----------|--------------------|-------|-----|------------------------|-------|---------|

| IC<br>Part<br>No. | Channel | BC1.2<br>&<br>APPLE | QC3.0<br>&<br>QC2.0 | FCP | SCP | AFC | SFCP     | MTK PE+<br>2.0&1.1 | USB C | NTC | QC<br>Certi-<br>ficate | PD3.0 | Package |

| IP2110            | 1       | V                   | -                   | -   | -   | -   | -        | -                  | -     | -   | -                      | -     | SOT23-5 |

| IP2111            | 1       | V                   | -                   | -   | -   | -   | -        | -                  | -     | -   | -                      | -     | SOT23-6 |

| IP2112            | 2       | V                   | -                   | -   | -   | -   | -        | -                  | -     | -   | -                      | -     | SOT23-6 |

| IP2161            | 1       | V                   | ٧                   | ٧   | -   | ٧   | v        | -                  | -     | -   | ٧                      | -     | SOT23-6 |

| IP2163            | 1       | V                   | ٧                   | ٧   | -   | ٧   | ٧        | ~                  | -     | ٧   | ٧                      | -     | SOP8    |

| IP2701            | 1       | v                   | ٧                   | ٧   | -   | ٧   | v        | -                  | v     | -   | -                      | -     | SOP8    |

| IP2703            | 1       | ٧                   | v                   | ٧   | -   | ٧   | v        | ٧                  | v     | v   | -                      | -     | DFN10   |

| IP2705            | 1       | ٧                   | v                   | ٧   | -   | ٧   | ٧        | v                  | ٧     | v   | -                      | -     | DFN12   |

| IP2707 | 2 | v | ٧ | ٧ | - | ٧ | ٧ | v   | ٧ | ٧ | - | - | QFN16 |

|--------|---|---|---|---|---|---|---|-----|---|---|---|---|-------|

| IP2716 | 1 | v | v | ٧ | v | ٧ | - | 1.1 | v | - | ٧ | v | QFN32 |

### 3. Absolute Maximum Ratings

| Parameters                                  | Symbol               | Value     | Unit |

|---------------------------------------------|----------------------|-----------|------|

| Input Voltage Range                         | $V_{IN}$ , $V_{BUS}$ | -0.3 ~ 16 | v    |

| Junction Temperature Range                  | TJ                   | -40 ~ 150 | C    |

| Storage Temperature Range                   | Tstg                 | -60 ~ 150 | °C   |

| Thermal Resistance<br>(Junction to Ambient) | $\theta_{JA}$        | 26        | °C/w |

| ESD (Human Body Model)                      | ESD                  | 4         | κν   |

\*Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability. \*Voltages are referenced to GND unless otherwise noted.

### 4. Recommended Operating Conditions

| Parameter       | Symbol                             | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------|------|------|------|------|

| Input Voltage   | V <sub>IN</sub> , V <sub>BUS</sub> | 4.5  | 5    | 14   | V    |

| Battery Voltage | Vbat                               | 3.0  | 3.7  | 4.5  | V    |

\*Devices' performance cannot be guaranteed when working beyond those Recommended Operating Conditions.

## 5. Electrical Characteristics

Unless otherwise specified, TA=25°C, L=2.2uH

| Parameter          | Symbol                              | Test Conditions          | Min. | Тур.     | Max. | Unit |

|--------------------|-------------------------------------|--------------------------|------|----------|------|------|

| Charging System    |                                     |                          |      |          |      |      |

| Input voltage      | V <sub>IN</sub><br>V <sub>BUS</sub> |                          | 4.5  | 5/7/9/12 | 13   | V    |

| Input Over Voltage | V <sub>IN</sub><br>V <sub>BUS</sub> |                          | 13   | 14       | 15   | V    |

|                    |                                     | R <sub>VSET</sub> = NC   | 4.16 | 4.2      | 4.24 | V    |

| Constant Charge    |                                     | R <sub>VSET</sub> = 120k | 4.31 | 4.35     | 4.39 | V    |

| Voltage            | V <sub>trgt</sub>                   | R <sub>VSET</sub> = 68k  | 4.36 | 4.4      | 4.44 | V    |

|                    |                                     | R <sub>VSET</sub> = 10k  | 4.46 | 4.5      | 4.54 | V    |

| Charge Current     | I <sub>CHRG</sub>                   | VIN =5V, input current   |      | 2.0      |      | А    |

|                                       |                           | VBUS =5V, input current                                             |       | 2.8  |       | А    |

|---------------------------------------|---------------------------|---------------------------------------------------------------------|-------|------|-------|------|

|                                       |                           | VIN or VBUS >=7V, input power                                       |       | 18   |       | W    |

| Trickle Charge Current                |                           | VIN=5V,BAT<1.5V                                                     | 50    | 100  | 150   | mA   |

| Trickle Charge Current                | I <sub>TRKL</sub>         | VIN=5V, 1.5V<=BAT<3.0V                                              | 100   | 250  | 400   | mA   |

| Trickle Charge Stop<br>Voltage        | V <sub>trkl</sub>         |                                                                     | 2.9   | 3    | 3.1   | v    |

| Charge Stop Current                   | I <sub>STOP</sub>         |                                                                     | 200   | 300  | 400   | mA   |

| Recharge Voltage<br>Threshold         | V <sub>RCH</sub>          |                                                                     | 4.08  | 4.1  | 4.13  | v    |

| Charge Safety Time                    | $T_{END}$                 |                                                                     | 20    | 24   | 27    | Hour |

| Boost System                          |                           |                                                                     |       | X    |       |      |

| Battery operation voltage             | V <sub>BAT</sub>          |                                                                     | 3.0   |      | 4.5   | v    |

| Battery input current                 | I <sub>BAT</sub>          | VBAT=3.7V,VOUT=5.1V,fs=375KHz                                       | 3     | 5    |       | mA   |

|                                       |                           | V <sub>OUT</sub> =5V@1A                                             | 4.95  | 5.12 | 5.23  | V    |

|                                       | QC2.0<br>V <sub>OUT</sub> | V <sub>out</sub> =9V@1A                                             | 8.75  | 9    | 9.25  | V    |

|                                       | - 001                     | V <sub>OUT</sub> =12V@1A                                            | 11.75 | 12   | 12.25 | V    |

| DC output voltage                     | QC3.0<br>V <sub>OUT</sub> | @1A                                                                 | 4.95  |      | 12.25 | v    |

|                                       | QC3.0<br>Step             |                                                                     |       | 200  |       | mV   |

| Output voltage ripple                 | Δν <sub>ουτ</sub>         | VBAT=3.7V,VOUT=5.0V,fs=375KHz                                       |       | 100  |       | mV   |

|                                       |                           | V <sub>OUT</sub> =5V                                                |       | 3.1  |       | А    |

| Boost output current                  | l <sub>out</sub>          | V <sub>OUT</sub> =9V                                                |       | 2.0  |       | А    |

|                                       |                           | V <sub>OUT</sub> =12V                                               |       | 1.5  |       | А    |

|                                       |                           | V <sub>BAT</sub> =3V, V <sub>OUT</sub> =5V, I <sub>OUT</sub> =2A    |       | 95   |       | %    |

| Boost efficiency                      | $\eta_{out}$              | V <sub>BAT</sub> =3V, V <sub>OUT</sub> =9V, I <sub>OUT</sub> =2A    |       | 92   |       | %    |

|                                       |                           | V <sub>BAT</sub> =3V, V <sub>OUT</sub> =12V, I <sub>OUT</sub> =1.5A |       | 90.8 |       | %    |

| Boost overcurrent shut down threshold | l <sub>shut</sub>         | VBAT=3.7V, 10mohm sample resistor at output                         | 3.5   | 3.8  | 4.0   | А    |

| Load overcurrent detect time          | T <sub>UVD</sub>          | Duration of output voltage under 4.2V                               |       | 30   |       | ms   |

| Load short circuit detect time        | T <sub>OCD</sub>          | Duration of output current above 4.2A                               | 150   |      | 200   | us   |

| Control System                        |                           |                                                                     |       |      |       |      |

|                                       |                           |                                                                     |       |      |       |      |

| Switch frequency                             | fs                                                    | Discharge switch frequency                                                           | 325 | 375                   | 425 | KHz |

|----------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----------------------|-----|-----|

| Switch frequency                             | 15                                                    | Charge switch frequency                                                              | 450 | 500                   | 550 | KHz |

| NMOS on resistance                           |                                                       | Upper NMOS                                                                           |     | 9                     | 11  | mΩ  |

| NMOS on resistance                           | r <sub>DSON</sub>                                     | Lower NMOS                                                                           |     | 9                     | 11  | mΩ  |

| VREG output voltage                          | $V_{\text{REG}}$                                      | VBAT=3.7V                                                                            | 3.0 | 3.1                   | 3.2 | V   |

| Battery port standby current                 | I <sub>STB</sub>                                      | VIN=0V, VBAT=3.7V, average current                                                   |     | 100                   |     | uA  |

| LDO output current                           | I <sub>LDO</sub>                                      |                                                                                      | 20  | 30                    | 40  | mA  |

| LED light driving<br>current                 | I <sub>WLED</sub>                                     |                                                                                      | 10  | 15                    | 20  | mA  |

| LED display driving<br>current               | Ι <sub>L1</sub><br>Ι <sub>L2</sub><br>Ι <sub>L3</sub> | Voltage decrease 10%                                                                 | 5   | 7                     | 9   | mA  |

| Light load shut down detect time             | T1 <sub>load</sub>                                    | Total load power lower than 300mW                                                    | 25  | 32                    | 44  | s   |

| Output port light load shut down detect time | T2 <sub>load</sub>                                    | Duration of voltage drop from VSN to<br>VOUT2 (or VOUT2, or VBUS) less<br>than 1.8mV |     | T1 <sub>load</sub> /2 |     | S   |

| Short press on key wake up time              | T <sub>OnDebounce</sub>                               |                                                                                      | 60  |                       | 500 | ms  |

| Time of WLED turn on                         | T <sub>Keylight</sub>                                 |                                                                                      | 1.2 | 2                     | 3   | s   |

| Thermal shut down temperature                | Тотр                                                  | Rising temperature                                                                   | 130 | 140                   | 150 | °C  |

| Thermal shut down hysteresis                 | ∆T <sub>otp</sub>                                     |                                                                                      |     | 40                    |     | °C  |

## 6. Function Description

#### Low power lock out and activation

The first time IP5328P access to the battery, whatever the battery voltage, IC is in lock out state, battery level indicator LED will flash four times; Under non-charging state, if the battery voltage is too low to trigger the low power shutdown, IP5328P will enter lock out state too.

Under the lock out state, to decrease the quiescent power, IP5328P do not support plug in detect function or key press activation function. During which, key press action will not trigger boost output, and battery level indicator LED will flash four times.

Under the lock out state, only by entering charging status can activate IP5328P's full function.

#### Charge

IP5328P integrated a constant current and constant voltage Li battery charging management system with synchronous switch, adaptive to various charging voltage.

When the battery voltage is lower than 3V, trickle charging less than 250mA charging current is applied; when the battery voltage is higher than 3V, enters constant current charging stage, the maximum charging current at battery port is 5.0A; when the battery voltage is near the preset battery voltage, enters constant voltage charging stage; when the charging current is less than 300mA and battery voltage is near the constant voltage charging stage, the charging process is stopped. When the charging stage is accomplished, once the battery voltage falls under 4.1V, battery charging stage will be restarted.

IP5328P adopted switch charging technology, switch frequency is 500kHz. During 5V input voltage, maximum input power is 10W; During the fast charging state, maximum input power is 18W. The highest charging current is up to 5.0A, charging efficiency can be up to 94%, such can reduce 3/4 charging time.

IP5328P will adjust charge current automatically applicable to adaptors with different load capacity.

IP5328P do not support charging the battery and phone at the same time, the output discharge port will be close while charging the battery, in case the input high voltage will take damage on the device under charge.

#### Boost

IP5328P Integrated a synchronized switch converter which supports high voltage output, providing 5V~12V output voltage output, load capacity can be: 5V/3.1A, 7V/2.4A, 9V/2.0A and 12V/1.5A. 375kHz switching frequency. Internal soft start function. In avoid of large rush current causing device failure at start up stage, built-in overcurrent, short circuit, overvoltage and over temperature protection function, make insurance of the stability and reliability of power system.

Boost system output current can be auto-modulated according to the temperature, ensuring the IC is under the preset temperature.

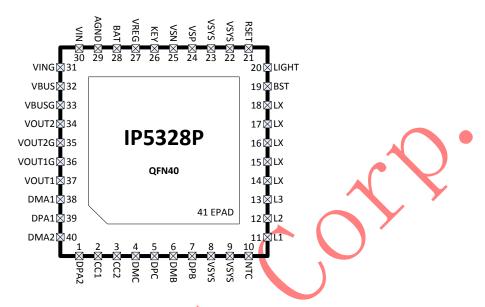

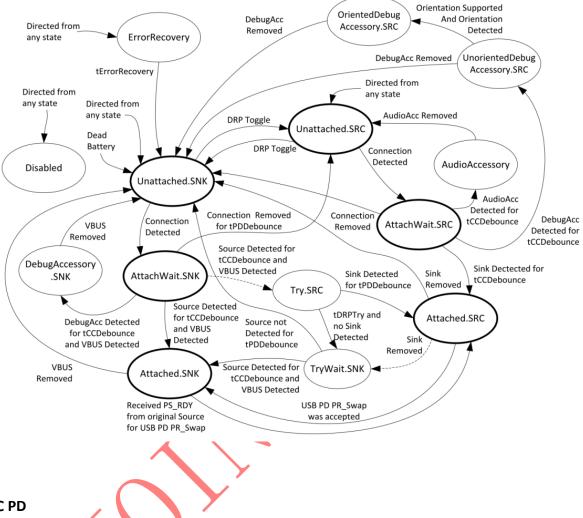

#### USB C

IP5328P integrated USB C DRP port, auto-switching the internal pull-up and pull-down circuit on CC1 and CC2 by distinguishing the role of the attached device. Support Try.SRC function, when the attached device is also DRP device, IP5328P will supply power for the opposite device.

When worked as DFP, the output current can be set as three levels; when worked as UFP, the current capability from the opposite device can be detected.

Comparator Threshold of pull-up Ip:

Table 4-23 CC Voltages on Source Side – 3.0 A @ 5 V

|                                   | Minimum Voltage | Maximum Voltage | Threshold |

|-----------------------------------|-----------------|-----------------|-----------|

| Powered<br>cable/adapter<br>(vRa) | 0.00 V          | 0.75 V          | 0.80 V    |

| Sink (vRd)                        | 0.85 V          | 2.45 V          | 2.60 V    |

| No connect<br>(vOPEN)             | 2.75 V          |                 |           |

Comparator Threshold of Pull-down Resistor Rd:

#### Table 4-25 Voltage on Sink CC pins (Multiple Source Current Advertisements)

| Detection   | Min voltage | Max voltage | Threshold |

|-------------|-------------|-------------|-----------|

| vRa         | -0.25 V     | 0.15 V      | 0.2 V     |

| vRd-Connect | 0.25 V      | 2.04 V      |           |

| vRd-USB     | 0.25 V      | 0.61 V      | 0.66 V    |

| vRd-1.5     | 0.70 V      | 1.16 V      | 1.23 V    |

| vRd-3.0     | 1.31 V      | 2.04 V      |           |

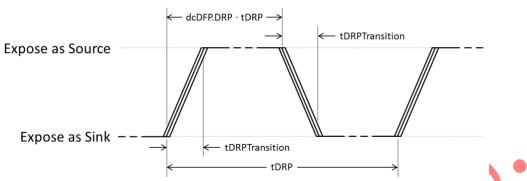

USB C detects cycle:

#### Figure 4-36 DRP Timing

Table 4-21 DRP Timing Parameters

|                | Minimum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Maximum                                                                                    | Description                                                                   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| tDRP 50 ms 10  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100 ms                                                                                     | The period a DRP shall complete a<br>Source to Sink and back<br>advertisement |

| dcSRC.DRP      | 30%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70% The percent of time that a DR advertise Source during tDRP                             |                                                                               |

| tDRPTransition | 0 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The time a DRP shall complet1 mstransitions between Source aSink roles during role resolut |                                                                               |

| tDRPTry        | 75 ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 150 ms                                                                                     | Wait time associated with the <u>Try.SRC</u> state.                           |

| tDRPTryWait    | tDRPTryWait 400 ms 800 ms Wait time associated with the time associated |                                                                                            | Wait time associated with the <u>Try.SNK</u> state.                           |

USB C detects state transition:

#### Figure 4-16 Connection State Diagram: DRP with Accessory and Try.SRC Support

#### USB C PD

IP5328P integrated USB C Power Delivery PD2.0/PD3.0/PPS (Programmable Power Supply) protocol, integrate physical (PHY) layer for data transmitting/receiving across the cc wire, hardware biphase mark coding (BMC) module and hardware CRC protect the data integrity.

Support PD2.0/PD3.0 bi-directional input/output and PPS output protocol. Input and output voltage support 5V/9V/12V PPS 5~12V output voltage adjustable with 20mV/step. Support up to 18W power level.

#### Fast Charge

IP5328P support several fast charge standards: QC2.0/QC3.0, FCP, AFC, SFCP, MTK, Apple, Samsung.

Input QC standard is not support for charging the power bank, if input QC standard is needful, the Qualcomm QC charging IC (SMB1351) is recommended.

Input fast charge standard of FCP, AFC, SFCP are supported for charging the power bank, because of the fast charging request is send on the DP/DM line, if other fast charge IC is applied, the FCP, AFC and SFCP fast charge cannot be supported at the same time.

If the power bank is to charge for the phone, when IP5328P enter discharge mode, it will detect the fast charge type and request on DP, DM, which support fast charge for devices of QC2.0/QC3.0, FCP, AFC, SFCP, MTK, and Apple 2.4A mode, Samsung 2.0A mode and BC1.2 1.0A mode.

For Apple 2.4A mode: DP=DM=2.7V

For Samsung 2.0A mode: DP=DM=1.2V

For BC1.2 1.0A mode: DP short to DM

Under BC1.2 mode, when the DP voltage is detected in the range of 2V~0.325V for 1.25s, fast charge will be initially determined, then the short status between DP and DM will be disconnected, and DM pull-down 20kOhm to GND at the same time. After which, if in the following 2ms the DP voltage is in range of 2V~0.325V and DM lower than 0.325V, fast charge handshake is accomplished successfully. Then QC2.0/QC3.0 device can request for desired voltage according to the QC standards. Any time DP lower than 0.325V will force to exit the fast charge mode, the ouput voltage will fall back to default 5V.

| DP   | DM           | Result          |  |  |

|------|--------------|-----------------|--|--|

| 0.6V | GND          | 5V              |  |  |

| 3.3V | 0.6V         | 9V              |  |  |

| 0.6V | 0.6V         | 12V             |  |  |

| 0.6V | 3.3V         | Continuous Mode |  |  |

| 3.3V | 3.3V sustain |                 |  |  |

|      |              |                 |  |  |

QC2.0/QC3.0 output voltage request rule:

Continuous mode is supported by QC3.0, voltage can be adjusted by 0.2V/step according to QC3.0 request under the continues mode.

#### Charge and Discharge Path Management

#### Standby:

If VIN or VBUS is attached to charge will start the charging process directly.

If USB C UFP device is attached on VBUS or sink device is attached on VOUT port, will start discharge function automatically.

If key is pressed, whether or not load is on VOUT1 port, VOUT1 port output will be force to open; but the VOUT2 and USB C port will open only when load is detected on the according port, or the output on these port will be closed. So VOUT1 must be retained if only one VOUT port is needed, if VOUT2 or VBUS is not needed, MOSFET can be eliminated, but the 10uF capacitor should be retained.

#### Discharge:

If key not pressed, only when sink device attached will the output port open, non-attached output port will not open. If the opened output port current is less than 180mA @ 10mOhm, it will wait for a period of time before close the port automatically. The output current is detected by the voltage drop between VSN to output, 180mA current is equivalent to 1.8mV on 10mOhm, when the resistance (including MOSFET internal resistance) between VSN and ouput is larger than 10mOhm, the current threshold will be decreased proportionally.

When only VOUT1 port opened, single short press on key do not take any effect; when VOUT2 or USB C is opened and in non-fast charge mode, single short press on key will force to open VOUT1 port; when VOUT2 or USB C is opened and in fast charge mode, the first single short press on key will force to close the fast charge on VOUT2 or USB C port, the second short press on key will force to open VOUT1 port, the time interval between the first and second short press should be longer than 1 second, otherwise will force to shut down the system.

Any one of the VOUT1, VOUT2 or USB C port support all the fast charge standards separately, but due to the single inductor design, only one output are support, only under single port opened situation fast charge is allowed. Two or more output port open at the same time, fast charge will be disabled automatically.

According to 'Typical Application Diagram', when one port is already in fast charge mode, if sink device is attached on another port (key press action is equal to VOUT1 load attached), all the output port together with the fast charge mode will be disabled firstly, then open the ports with sink device attached, after which all the ports only support Apple, Samsung and BC1.2 mode. If the sink device decreased from multiple to one and keep this situation for 16s, all the output ports will be closed firstly (pay special attention to PCB layout routing for this case, otherwise will lead to failure on restore of fast charge function, please refer to 'PCB Layout'), and then the high voltage fast charge function are enabled, then the output port of the only one sink device attached will be opened, such that will re-activate the sink device to send fast charge request . when only one port is opened, if the total power is lower than 300mW for about 32s, the output port and discharge will be closed and the system enters low standby mode.

#### Charging:

When power are applied on either VIN or VBUS port can activate the IP5328P enter charging process, if both ports are applied at the same time, USB C port power will be used for charging in priority.

if additional input fast charge IC are needed, 2 back-to-back PMOS should be applied on the added input port for power partition control, in case current flow from high voltage port to low voltage port when two ports attached at the same time.

In single port charging mode, the fast charge mode can be distinguished automatically, appropriate voltage and current will be auto matched.

Standard solution do not support charging the sink device and battery at the same time, during charging mode, even if sink devices are attached on the output port, the output port will not be opened. But if battery is fully charged and the charging power supply is not detached, IP5328P will open the output port for the sink device on the premise of 5V voltage on the charging port.

#### Charging and discharging at the Same Time (Customized Solution):

In this customized solution, RSET function is not available; the RSET is redefined as an indicator of this customized mode. If IP5328P are in charging the battery and sink device at the same time, RSET will output high voltage, otherwise RSET will output low voltage.

When the charging power supply and sink device are attached at the same time, IP5328P will charge the battery and sink device at the same time. Under this mode, IP5328P will disable the input fast charge function ( if the additional fast charge IC is applied , RSET pin is used to control the enable pin of the additional fast charge IC), when VSYS is only 5V, the discharge path will be enabled for the sink device. If the VSYS voltage is higher than 5.8V, for safety consideration, the discharge path will be disabled. To make insurance of the normal charging and high priority of charging the sink device, IP5328P will increase the charging under voltage threshold to 4.9V.

During the process of charging and discharging at the same time, if the input charging power supply is unplugged, IP5328P will disable the input charging function and restart the discharge function for the sink device. For safety consideration and to re-activate the sink device to send fast charge request, the voltage will fall to 0 during this conversion process.

During the process of charging and discharging at the same time, if the discharging sink device is unplugged or the sink device stop to sink current for 16s, the discharge path will be closed automatically. When all the discharge paths are disabled and return to single port charge state, the under voltage threshold will be decreased, fast charge for the power bank will be auto re-activated.

#### Auto detection on sink device/phone attachment

IP5328P support auto detection on sink device/phone attachment/ plug in, once the attachment is detected, the boost will be turned on charging the sink device/phone, so non-key solution are supported.

#### Auto detection on sink device/phone fully charged

IP5328P detect the current output current through off-chip 10mOhm resistor, when the total power is lower than 300mW for 32s, IP5328P will consider all the output port is plug out, the output voltage will be closed then.

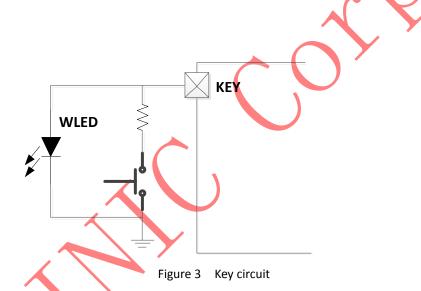

Key

Key circuit is illustrated in Figure 3, which can recognize short press or long press operation.

- Short press (pressed time in range of 60ms~2s): turn on the battery level display LED and BOOST output

- Long press (pressed time longer than 2s): turn on or turn off the torch light WLED

- No response on press time less than 30ms

- Two short press in 1s: turn off boost output, battery level display LED and torch light WLED

Long 10s press will reset the whole system

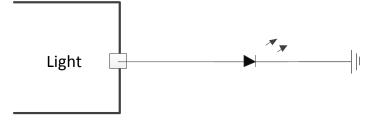

#### Fast Charge state indication

Light is used for indication for the present fast charge mode, either in fast charging or discharging mode, when the system enters fast charge mode and in non-5V mode, the light LED will turn on.

#### **Coulombmeter and battery level display**

Built-in coulombmeter support battery capacity calculation without measuring the current on the BAT pin.

IP5328P support 1/2/3/4 LED display solution, by internal intelligent algorithm, the LED applied outside can be distinguished by IP5328P.

| 50%≤C<75%                                                                        | ON          | ON  | ON  | OFF |

|----------------------------------------------------------------------------------|-------------|-----|-----|-----|

| 25%≤C<50%                                                                        | ON          | ON  | OFF | OFF |

| 3%≤C<25%                                                                         | ON          | OFF | OFF | OFF |

| 0% <c<3%< td=""><td>1.0Hz Flash</td><td>OFF</td><td>OFF</td><td>OFF</td></c<3%<> | 1.0Hz Flash | OFF | OFF | OFF |

| C=0%                                                                             | OFF         | OFF | OFF | OFF |

#### 3 LED display:

During charging:

| Battery capacity (C) (%) | D1          | D2          | D3          |          |

|--------------------------|-------------|-------------|-------------|----------|

| Fully charged            | ON          | ON          | ON          | Y        |

| 66%≤C                    | ON          | ON          | 1.5Hz Flash | <b>Y</b> |

| 33%≤C<66%                | ON          | 1.5Hz Flash | OFF         |          |

| C<25%                    | 1.5Hz Flash | OFF         | OFF         |          |

#### During discharging:

| Battery capacity (C) (%)                                             | D1          | D2  | D3  |

|----------------------------------------------------------------------|-------------|-----|-----|

| C≥66%                                                                | ON          | ON  | ON  |

| 33%≤C<66%                                                            | ON          | ON  | OFF |

| 3%≤C<33%                                                             | ON          | OFF | OFF |

| 0% <c<3%< td=""><td>1.0Hz Flash</td><td>OFF</td><td>OFF</td></c<3%<> | 1.0Hz Flash | OFF | OFF |

| C=0%                                                                 | OFF         | OFF | OFF |

2 LED display mode 1 is bi-color LED:

#### During charging

|   | Battery capacity (C) (%) | D1          | D2          |

|---|--------------------------|-------------|-------------|

|   | Fully charged            | OFF         | ON          |

|   | 66%≤C<100%               | OFF         | 1.5Hz Flash |

| Y | 33%≤C<66%                | 1.5Hz Flash | 1.5Hz Flash |

|   | C<33%                    | 1.5Hz Flash | OFF         |

#### During discharging:

| Battery capacity (C) (%) | D1  | D2  |

|--------------------------|-----|-----|

| 66%≤C<100%               | OFF | ON  |

| 33%≤C<66%                | ON  | ON  |

| C<33%                    | ON  | OFF |

| C<3% | 1.0Hz Flash | OFF |

|------|-------------|-----|

|------|-------------|-----|

#### 2 LED mode 2 display:

During charging: D1 LED flash on cycle of 2s (1s on and 1s off), when fully charged, constantly on; During discharging: D2 LED is constantly on, when voltage lower than 3.2V, flash on cycle of 1s (0.5s on and 0.5s off), when voltage is lower than 3.0V, system is power down.

1 LED mode 1 display:

During charging: LED flash on cycle of 2s (1s on and 1s off), when fully charged, constantly on; During discharging: LED is constantly on, when voltage lower than 3.2V, flash on cycle of 1s (0.5s on and 0.5s off), when voltage is lower than 3.0V, system is power down.

#### RSET (Battery internal resistor set)

The internal resistor of the battery can be set by RSET pin, the charging and discharging threshold voltage on LED will be changed at the same time, accordingly the uniformity of the LED display on the battery level are adjusted at the same time.

|                      | RSET resistor (Kohm) | Battery internal resistance set(mOhm) |  |  |  |  |  |

|----------------------|----------------------|---------------------------------------|--|--|--|--|--|

|                      | >179                 | 93.75                                 |  |  |  |  |  |

|                      | 169~179              | 87.5                                  |  |  |  |  |  |

|                      | 159~169              | 81.25                                 |  |  |  |  |  |

|                      | 149~159              | 75                                    |  |  |  |  |  |

|                      | 139~149              | 68.75                                 |  |  |  |  |  |

|                      | 129~139              | 62.5                                  |  |  |  |  |  |

|                      | 119~129              | 56.25                                 |  |  |  |  |  |

| <ul> <li></li> </ul> | 109~119              | 50                                    |  |  |  |  |  |

|                      | 99~109               | 43.75                                 |  |  |  |  |  |

|                      | 89~99                | 37.5                                  |  |  |  |  |  |

| Y                    | 79~89                | 31.25                                 |  |  |  |  |  |

| Y                    | 69~79                | 25                                    |  |  |  |  |  |

| •                    | 59~69                | 18.75                                 |  |  |  |  |  |

|                      | 49~59                | 12.5                                  |  |  |  |  |  |

|                      | 39~49                | 6.25                                  |  |  |  |  |  |

|                      | 0~39                 | 0                                     |  |  |  |  |  |

|                      |                      |                                       |  |  |  |  |  |

#### VSET (battery type set)

Battery type can be set by the VSET pin, accordingly, the battery level display threshold voltage and Constant Voltage charging threshold voltage are changed at the same time. VSET resistor and battery type are listed below:

| VSET resistor (Kohm) | Battery type |

|----------------------|--------------|

| NC                   | 4.2V         |

| 120                  | 4.35V        |

| 68                   | 4.4V         |

| 10                   | 4.5V         |

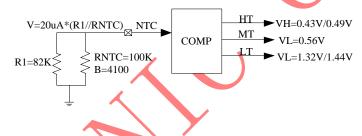

#### NTC

IP5328P support NTC function used for battery temperature detection. NTC pin output 20uA current then detect the voltage on NTC pin to determine the present battery temperature.

Figure 5 Battery NTC comparator

#### Under charging state:

Voltage on NTC pin is 1.32V meaning the battery temperature is low 0 centigrade, stop charging the battery; Voltage on NTC pin is 0.56V meaning the battery temperature is medium 45 centigrade, charging current half down;

Voltage on NTC pin is 0.49V meaning the battery temperature is medium 50 centigrade, stop charging the battery;

#### Under discharging state:

Voltage on NTC pin is 1.44V meaning the battery temperature is low -15 centigrade, stop discharging;

Voltage on NTC pin is 0.43V meaning the battery temperature is high 55 centigrade, stop discharging;

If NTC is not needed, NTC should serial a 51kOhm resistor to ground, do not float NTC or tie it to ground directly.

#### VREG

VREG is a normally opened 3.1V LDO, load capacity is 30mA.

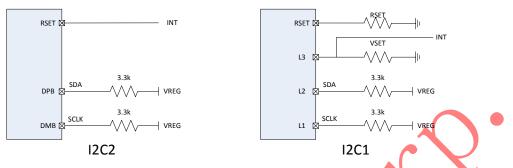

#### 12C

I2C connection:

IP5328P support to connect with I2C1 or I2C2 at a time, when I2C circuit is deployed, the two pins will work as I2C\_SDA and I2C\_SCLK and the reused function will be disabled. Under I2C mode, INT signal is high-z at standby and high level at working state, which is used for waking up the MCU.

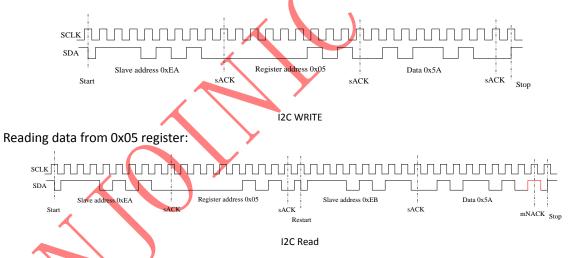

I2C support up to 400Kbps transfer rate, 8-bit address and 8-bit data, MSB on rending and receiving. Device address is 0xEA for write, 0xEB for read.

For example:

Writing data into 0x05 register:

Under I2C mode, RSET is low level when IP5328P is power down and high level when IP5328P is power up, thus RSET can be used for MCU wake up.

### 7. PCB Layout

Here below lists essential precautions that may affect the function and performance on PCB layout, more details will be attached in another document if any.

#### Location of VSYS capacitor

Both power and current is large under normal operating, location of capacitor on VSYS net affects the stability of DCDC. VSYS capacitor should be placed as close to VSYS pin and EPAD as possible, deploy large copper pour and add more vias, decrease the area of current loop between capacitor and IC and reduce the parasitic parameter.

VSYS pin distribute at two sides of the IC, capacitor should be placed on each side and connect the two pins with wide (wider than 100mil) copper on PCB board.

#### 10mOhm sample resistor

IP5328P sample the current on 10mOhm between VSN and VSP pin to take control of input charging current, output overcurrent protection, output light load power down. VSN and VSP tracks should keep away from signals that may generate large interference, lay to the 10mOhm resistor separately, do not overlay with other current track or VSYS track. Though VSP and VSYS are same net on PCB, layout of those two pins should be separated.

To enhance the immunity of interference of sample signal, 100nF filter capacitor are needed on VSN and VSP pins and place as close as possible.

The layout is illustrated below:

#### Layout from 10mOhm sample resistor to input/output MOSFET

Application example: non-fast charge phone is attached VOUT1, fast charge phone is attached on VOUT2, this is multiple output ports case, IP5328P will output 5V for both phones. When VOUT1 is plug out or power consumption is lower than the preset value, IP5328P will disable VOUT1 output and maintain VOUT2 output, fast charge output will be re-activated and supplied on VOUT2.

To realize the self-recovery of fast charge, output current on VOUT1 port should be detected accurately. This current is detected by measuring the voltage drop between VSN and VOUT1 pin, the precondition of closing the VOUT1 port is voltage drop lower than 1.8mV. So no other current tack is allowed to flow through VSN and VOUT1, or false current will form voltage drop and lead to erroneous judgment on current. Similarly, pay special attention on the other output ports.

Above all, lay separately on 10mOhm to VOUT1, 10mOhm to VOUT2 and 10mOhm to VIN on PCB independently, any two current tracks should not overlay, if not, self-recovery of fast charge function in the application example above may fail now and then.

The layout example is demonstrated below:

If improper layout lead to 1mOhm overlayed track on VOUT1 and VOUT2 output current, 2A current on VOUT2 output will bring in 2mV voltage drop on the 1mOhm overlayed track. In this case, IP5328P cannot judge if VOUT1 still has device attached even though device is plug out, thus lead to a failure on recovery of fast charge function on VOUT2. Only when the output current on VOUT2 port is lower than 1.8A, and the corresponding voltage drop on 1mOhm overlayed track is lower than 1.8V, can VOUT2 fast charge function be re-activated.

### 8. Typical Application Diagram

Total solution of fast charge power bank is merely realized by passive devices of MOSFET, inductor, capacitor and resistor.

If only one VOUT is needed, preserve VOUT1

USB C, Q2 PMOS and R8 can be eliminated, retain CP10

### **BOM List**

| No. | Part Name                 | Туре               | Location             | Num | Note                           |

|-----|---------------------------|--------------------|----------------------|-----|--------------------------------|

| 1   | SMT IC                    | QFN40 IP5328P      | U1                   | 1   |                                |

| 2   | SMT capacitor             | 0603 100nF 10% 25V | C3 C4                | 3   |                                |

| 3   | SMT capacitor             | 0603 2.2uF 10% 16V | C1 C2                | 2   |                                |

| 4   | SMT capacitor             | 0805 22uF 10% 16V  | CP1 CP2 CP3<br>CP14  | 4   |                                |

| 5   | SMT capacitor             | 0805 22uF 10% 25V  | CP4 CP5 CP6<br>CP8   | 4   |                                |

| 6   | SMT capacitor             | 0805 10uF 10% 25V  | CP7 CP9 CP10<br>CP13 | 4   |                                |

| 7   | electrolytic<br>capacitor | 220uF 25V 10%      | CP12                 | 1   | <b>)</b>                       |

| 8   | SMT resistor              | 1206R 0.01R 1%     | R1                   | 1   |                                |

| 9   | SMT resistor              | 0603R 20R 5%       | R4                   | 7   | Adjust brightness of the light |

| 10  | SMT resistor              | 0603R 100R 5%      | R2 R5 R7             | 3   |                                |

| 11  | SMT resistor              | 0603R 1K 5%        | R6                   | 1   |                                |

| 12  | SMT resistor              | 0603R 10K 5%       | R8 R9                | 2   |                                |

| 13  | SMT resistor              | 0603R 110K 1%      | R10                  | 1   |                                |

| 14  | SMT resistor              | 0603R 82K 1%       | R12                  | 1   | For NTC only                   |

| 15  | NTC thermal resistor      | 100K@25℃ B=4200    | RNTC                 | 1   | For NTC only                   |

| 16  | SMT LED                   | 0603 blue LED      | D1 D2 D3 D4          | 4   |                                |

| 17  | SMT LED                   | 0603 green LED     | D8                   | 1   |                                |

| 18  | LED light                 | 5MM LED            | D5                   | 1   |                                |

| 19  | SMT inductor              | 2.2uH 10*10        | L1                   | 1   |                                |

| 20  | SMT NMOS                  | SOT23-3 RU207C     | Q1 Q3                | 2   | Rds(on)<20m ohm I>=4A          |

| 21  | SMT PMOS                  | SOT23-3 RU20P7C    | Q2 Q4                | 2   | Rds(on)<20m ohm I>=4A          |

| 22  | USB C port                | USB C port         | J1                   | 1   |                                |

| 23  | key                       | SMT 3*6 key        | SW1                  | 1   |                                |

| 24  | Output USB                | AF10 8 pin USB     | USB1 USB3            | 2   |                                |

| 25  | Input USB                 | MICRO-7-DIP-5.9    | USB2                 | 1   |                                |

Recommended inductor type:

|                |           |                    |           | C          | C    | Heat Rating | Saturation  |             |

|----------------|-----------|--------------------|-----------|------------|------|-------------|-------------|-------------|

| DARFON PIN     | Thickness | Inductance<br>(uH) | Tolerance | Resistance |      | Current     | Current     | Measuring   |

|                | (mm)      |                    |           | (mΩ)       |      | DC Amp.     | DC Amps.    | Condition   |

|                |           |                    |           | Тур.       | Max. | ldc(A)Max.  | Isat(A)Max. |             |

| SPM70702R2MESQ | 5         | 2.2                | ±20%      | 9          | 10.2 | 10.5        | 13.5        | 100kHz/1.0V |

| SPM10102R2MESN | 4         | 2.2                | ±20%      | 6          | 7    | 12          | 18          | 100kHz/1.0V |

| SHC1004-2R2M   | 4         | 2.2                | ±20%      | 7          | 9    | 12          | 24          |             |

### 9. Package

### **10.Certificate Information**

#### QUALCOMM® QUICK CHARGE™ 3.0 TECHNOLOGY

1/1

#### HIGH VOLTAGE DEDICATED CHARGING PORT VERIFICATION

#### ISSUED BY UL TAIWAN CO., LTD.

| CERTIFICATE NO        | ▶ 4788056908-2                                                        |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| SPECIFICATION         | Qualcomm HVDCP Interface Specification Revision K                     |  |  |  |  |  |

| APPROVAL DATE         | December 14, 2017                                                     |  |  |  |  |  |

| APPROVAL TYPE         | ORIGINAL ASSESSMENT                                                   |  |  |  |  |  |

|                       | INJOINIC TECHNOLOGY                                                   |  |  |  |  |  |

| CERTIFICATE HOLDER    | Room 1301, Unit A2, Kexing Science Park, Keyuan Road NO.15, Nanshan   |  |  |  |  |  |

|                       | <ul> <li>District, Shenzhen, Guangdong, China</li> </ul>              |  |  |  |  |  |

| TYPE OF EQUIPMENT     | Chipset Reference Design                                              |  |  |  |  |  |

| TRADE NAME AND MODEL  | INJOINIC TECHNOLOGY                                                   |  |  |  |  |  |

| I RADE NAME AND MODEL | ▶ IP5328                                                              |  |  |  |  |  |

|                       | MEASUREMENT FACILITIES                                                |  |  |  |  |  |

| LABORATORY NAME AND   | UL Verification Services (Guangzhou) Co., Ltd., Song Shan Lake Branch |  |  |  |  |  |

|                       | Building 10, Innovation Technology Park, Song Shan Lake               |  |  |  |  |  |

| ADDRESS               | <ul> <li>Hi-Tech Development Zone, Dongguan, 523808, China</li> </ul> |  |  |  |  |  |

|                       |                                                                       |  |  |  |  |  |

Verification of equipment means only that the equipment has met the requirements of the above-noted specification. Trademark applications and agreements regarding the use of Quick Charge 3.0 Logo, are acted on accordingly by Qualcomm Technologies, Inc. This certificate is issued on condit that the holder complies and will continue to comply with the Quick Charge 3.0 program requirements established by Qualcomm Technologies, Inc. The equipment for which this certificate is issued shall not bear the Qualcomm Quick Charge 3.0 Logo unless the equipment complies with the applicable technical specifications and agreements issued by Qualcomm Technologies, Inc. as applicable to the Type Of Equipment designated above.

I hereby attest that the subject equipment was tested and found in compliance with the above-noted specification.

**ISSUED BY:**

Chiang Danie/

DANIEL CHIANG PROJECT ENGINEER, UL Taiwan Co., Ltd.

**ISSUED ON:**

December 14, 2017

UL TAIWAN CO., LTD. Tel: +886.2.7737.3000 1/F, 260, Da-Yeh Road, Peitou, Taipei, Taiwan 112 www.ul.com

# **IMPORTANT NOTICE**

INJOINIC TECHNOLOGY and its subsidiaries reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to INJOINIC TECHNOLOGY's terms and conditions of sale supplied at the time of order acknowledgment.

INJOINIC TECHNOLOGY assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using INJOINIC TECHNOLOGY's components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of INJOINIC TECHNOLOGY's components in its applications, notwithstanding any applications-related information or support that may be provided by INJOINIC TECHNOLOGY. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify INJOINIC TECHNOLOGY and its representatives against any damages arising out of the use of any INJOINIC TECHNOLOGY's components in safety-critical applications.

Reproduction of significant portions of INJOINIC TECHNOLOGY's information in INJOINIC TECHNOLOGY's data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. INJOINIC TECHNOLOGY is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

INJOINIC TECHNOLOGY will update this document from time to time. The actual parameters of the product may vary due to different models or other items. This document voids all express and any implied warranties.

Resale of INJOINIC TECHNOLOGY's components or services with statements different from or beyond the parameters stated by INJOINIC TECHNOLOGY for that component or service voids all express and any implied warranties for the associated INJOINIC TECHNOLOGY's component or service and is an unfair and deceptive business practice. INJOINIC TECHNOLOGY is not responsible or liable for any such statements.